S.-L. Wang, J.-W. Yu, P.-C. Yeh, H.-W. Kuo, L.-H. Peng et al.

**Applied Physics**

Letters

Citation: Appl. Phys. Lett. **100**, 063506 (2012); doi: 10.1063/1.3683518 View online: http://dx.doi.org/10.1063/1.3683518 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v100/i6 Published by the American Institute of Physics.

## **Related Articles**

Kelvin probe microscopic visualization of charge storage at polystyrene interfaces with pentacene and gold APL: Org. Electron. Photonics 5, 45 (2012)

Note: A high dynamic range, linear response transimpedance amplifier Rev. Sci. Instrum. 83, 026106 (2012)

Kelvin probe microscopic visualization of charge storage at polystyrene interfaces with pentacene and gold Appl. Phys. Lett. 100, 073305 (2012)

Development of high-voltage pulse-slicer unit with variable pulse duration for pulse radiolysis system Rev. Sci. Instrum. 83, 024709 (2012)

Magnetic-field effects in illuminated tetracene field-effect transistors Appl. Phys. Lett. 100, 073304 (2012)

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

## ADVERTISEMENT

■LakeShore Model 8404 **TOYO** Corporation NEW AC/DC Hall Effect System Measure mobilities down to 0.001 cm²/Vs

## High mobility thin film transistors with indium oxide/gallium oxide bi-layer structures

S.-L. Wang,<sup>1</sup> J.-W. Yu,<sup>1</sup> P.-C. Yeh,<sup>1</sup> H.-W. Kuo,<sup>1</sup> L.-H. Peng,<sup>1,a)</sup> A. A. Fedyanin,<sup>2</sup> E. D. Mishina,<sup>3</sup> and A. S. Sigov<sup>3</sup>

<sup>1</sup>Department of Electrical Engineering, Institute of Photonics and Optoelectronics, and Center for Emerging Materials and Advanced Devices, National Taiwan University, Taipei 106, Taiwan <sup>2</sup>Faculty of Physics, Lomonosov Moscow State University, Moscow 119991, Russia <sup>3</sup>Moscow State Technical University of Radioengineering, Electronics, and Automation, Moscow 119454, Russia

(Received 23 November 2011; accepted 18 January 2012; published online 9 February 2012)

We investigate the transport properties of thin-film transistors using indium oxide  $(In_2O_3)/gallium$  oxide  $(Ga_2O_3)$  bi-layer stacks as the channel material. At low gate bias, we observe the transistor field-effect mobility increases with the film resistivity to  $\mu_{FE} = 51.3 \text{ cm}^2/\text{Vs}$  and ON/OFF current ratio to  $10^8$  due to combinatorial layer thickness modulation. With the Ga<sub>2</sub>O<sub>3</sub> layer thickness ratio increase to R = 14.35%, these observations are accompanied with one-order-of-magnitude reduction in the transistor subthreshold swing to 0.38 V/decade and suggest a trap-limited conduction mechanism upon which the reduced scattering centers due to annihilation of subgap states improve the device electric characteristics without post-growth annealing. © 2012 American Institute of Physics. [doi:10.1063/1.3683518]

Thin film transistors (TFTs) are an essential element for flat-panel displays and next-generation microelectronic devices.<sup>1</sup> Hydrogenated amorphous silicon (a-Si:H) has been one of the widely used channel materials for TFTs. However, it suffers from issues such as low mobility ( $\mu < 1 \text{ cm}^2/\text{Vs}$ ) and instability under illumination and electric bias stress.<sup>2</sup> Alternative TFT channel design, comprising a superlattice structure made of hydrogenated silicon nitride (a-Si<sub>3</sub>N<sub>4</sub>:H)/ a-Si:H, has been proposed to increase the mobility by a factor of 5 due to the quantization effect.<sup>2</sup> Recent study on amorphous indium-gallium-zinc-oxide (a-IGZO),<sup>3</sup> and their derivatives of a-IGO and a-IZO have drawn interest due to superior carrier mobility  $(\mu > 10 \text{ cm}^2/\text{Vs})^4$  and low temperature processing.<sup>5</sup> Conventional wisdom suggests that the high carrier density in oxide semiconductors can be related to oxygen vacancies (V<sub>O</sub>) and other native defects. Model analysis indicates that carrier transport is controlled by multiple trap-and-release events when the device is biased at low gate voltage with the Fermi level residing within the localized tail states.<sup>6</sup> The percolation conduction mechanism prevails when carriers are released to the non-localized states and find the paths of least resistance. Wave function overlap between the s-orbitals of the adjacent In cations can make the carrier transportation insensitive to structure disorder, thus leading to high field-effect mobility ( $\mu_{\rm FE}$ ) in the oxidebased TFTs.<sup>7</sup> It was also noted that the formation energy of Vo increases with Ga atoms, which can suppress the O-deficiency related defects and improve device stability.<sup>8,9</sup> These observations outline a possibility to tailor the electric properties of oxide TFTs by adding Ga ions to enhance the material amorphization using the techniques such as sputtering<sup>10</sup> or solution-base process.<sup>11</sup>

Here, we demonstrate another aspect of engineering the transport properties of oxide TFTs by mitigating the trap density of subgap states (Dsg) in the In2O3/Ga2O3 bi-layer system. We note that as the Ga<sub>2</sub>O<sub>3</sub> layer thickness ratio R, defined as  $tGa_2O_3/(tGa_2O_3 + tIn_2O_3)$ , increases from 11% to 25%, the equivalent film resistivity ( $\rho_{eff}$ ) can span a wide range from 10<sup>4</sup> to 10<sup>7</sup>  $\Omega$  cm with a rate of 5.35% ± 0.05%/ decade. From bottom-gate TFTs made of such In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> bi-layer stack, we achieve a peak field-effect mobility  $\mu_{\rm FE} = 51.3 \text{ cm}^2/\text{Vs}$ , ON/OFF current ratio of 10<sup>8</sup>, and threshold voltage  $V_T = 0.57$  V at a Ga<sub>2</sub>O<sub>3</sub> layer thickness ratio R = 14.35% ( $\rho_{eff} = 9.2 \times 10^4 \ \Omega$  cm). These data are taken without post-growth annealing and concurred with an order of magnitude reduction in the TFT subthreshold swing to S = 0.38 V/decade. Such behavior can be ascribed to a mechanism of suppression of subgap trap density D<sub>sg</sub> in thin  $In_2O_3$  layers when interfaced to  $Ga_2O_3$ .<sup>8,9</sup>

The preparation of  $In_2O_3/Ga_2O_3$  bi-layer stack materials used in this study was facilitated by the sputtering method at a temperature below 60 °C. The materials were typically grown at a sputtering power of 70 W and working pressure of 4 mTorr, with flow rate of argon (Ar)/oxygen (O<sub>2</sub>) fixed at 30/30 sccm (standard cubic centimeter per minute). Under these conditions, a growth rate of 0.14 Å/s and 0.09 Å/s, respectively, can be found for depositing the In<sub>2</sub>O<sub>3</sub> and Ga<sub>2</sub>O<sub>3</sub> films on quartz substrates. A transmission line method (TLM),<sup>12</sup> with electrode patterns composed of 200 nm-thick molybdenum (Mo) stripes of 4 to 16  $\mu$ m spacing, was applied to characterize  $\rho_{eff}$ .

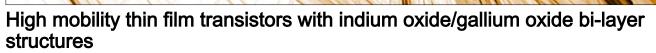

Shown in the inset of Fig. 1(a) are the resistance data taken on sample 1 designed to have 7 pairs of  $In_2O_3/Ga_2O_3$  stack with 3.5/0.57 nm layer thickness in each pair. From a linear slope fitting of the resistance data to the Mo stripe spacing, one can extract  $\rho_{eff}$  by considering a multiplication factor of film thickness. This process allows us to examine the  $\rho_{eff}$  distribution associated with various  $In_2O_3/Ga_2O_3$

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: peng@cc.ee.ntu.edu.tw.

FIG. 1. (Color online) (a) The effective channel resistivity ( $\rho_{eff}$ ) for In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> devices fixed with 3.5 nm-thick In<sub>2</sub>O<sub>3</sub> but varied in the Ga<sub>2</sub>O<sub>3</sub> layer thickness, inset: TLM data on device with 3.5/0.57 nm In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub>, and (b) dependence of  $\rho_{eff}$  on the Ga<sub>2</sub>O<sub>3</sub> thickness ratio according to the In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> layer structures listed in Table I.

layer thickness combination. Referred to Fig. 1(a), logarithmic increase in  $\rho_{eff}$  at a rate of 5.35%  $\pm$  0.05%/decade is observed on samples fixed with 3.5 nm-thick In<sub>2</sub>O<sub>3</sub> layers but varied in the Ga<sub>2</sub>O<sub>3</sub> layer thickness. Similar increasing rate can also be found in Fig. 1(b) according to the In<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> layer thickness variation listed in Table I. With oxygen partial pressure *fixed* in our experiments, these analyses illustrate wide range of resistivity tunability (10<sup>4</sup> to 10<sup>7</sup>  $\Omega$  cm) in the In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> multi-layer system due to layer thickness modulation.

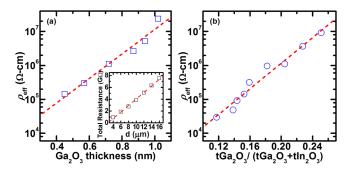

A plausible mechanism to the aforementioned phenomena is due to the mitigation of trap density of subgap states in the In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> system.<sup>8,9</sup> The latter was examined by applying a high-low frequency capacitance analysis<sup>13</sup> to a metal insulator semiconductor capacitor (MIS-cap) device due to less parasitic circuit components than its TFT counterpart.14 Two capacitor devices were prepared: MIS-cap A with a 30 nm-thick In<sub>2</sub>O<sub>3</sub> single layer and MIS-cap B with an additional 2 nm-thick Ga<sub>2</sub>O<sub>3</sub> layer deposited to In<sub>2</sub>O<sub>3</sub> (Fig. 2(a)). These MIS-cap devices were fabricated on Mocovered quartz substrates using 40 nm- and 200 nm-thick Si<sub>3</sub>N<sub>4</sub> and Mo layers as the insulator and top/bottom electrodes. Here the low-frequency (lf, 50 Hz) and high-frequency (hf, 100 KHz) capacitance data were measured as a function of the bias voltage and normalized to that  $(C_i = 17.9 \text{ pf})$  of Si<sub>3</sub>N<sub>4</sub> gate capacitance. A first glance of data shown in Fig. 2(b) depicts a positive shift of the C-V curves of MIS-cap device B to those of MIS-cap device A. It reveals a combined effect due to change in the flat-band voltage and work function difference in the single-layer In<sub>2</sub>O<sub>3</sub> and bi-layer In<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> structure.<sup>13</sup> Stretch-out of the high-frequency C-V component with respect to its low-frequency counterpart signifies a subtlety that the interfacial traps/charges do not follow the high-frequency modulation signal such that the capacitance value slowly varies with the gate bias  $(V_G)$ .

One can further extract the interfacial trap density  $D_{it}$  with Eq. (1),<sup>13</sup> where  $C_i$  is the insulator (Si<sub>3</sub>N<sub>4</sub>) capacitance and  $C_{lf}/C_{hf}$  the low/high frequency, respectively.

$$D_{it} = (1/q) \{ [(1/C_{lf}) - (1/C_i)]^{-1} - [(1/C_{hf}) - (1/C_i)]^{-1} \}.$$

(1)

Referred to the inset of Fig. 2(b), our analysis indicates that an order of magnitude reduction in the peak value of  $D_{it}$ , varying from  $\sim 2 \times 10^{13}$  to  $\sim 2 \times 10^{12}$  eV<sup>-1</sup> cm<sup>-2</sup> at V<sub>G</sub> > 0, can be achieved when a 2 nm-thick Ga<sub>2</sub>O<sub>3</sub> layer is added to an In<sub>2</sub>O<sub>3</sub> MIS-cap device.

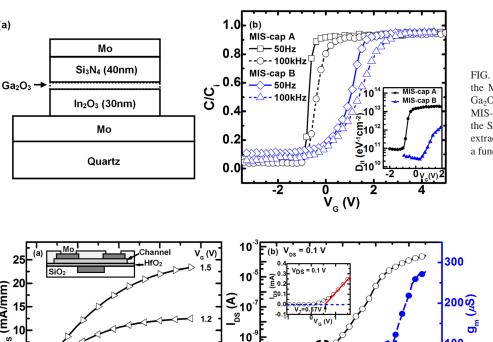

These observations highlight a promising use of  $In_2O_3/Ga_2O_3$  bi-layer channel for TFT operation. As a proof, another set of TFTs was fabricated according to the layer thickness variation listed in Table I. A device cross-sectional view is shown in the inset of Fig. 3(a). First, the quartz substrate was etched to a depth of ~70 nm followed by Mo-layer deposition which serves as the bottom-gate electrode. A 9 nm-thick hafnium oxide (HfO<sub>2</sub>) layer was then deposited on the Mocovered quartz substrate using an atomic layer deposition method. The drain/source contacts were made of 200 nmthick Mo layers. The device surface was passivated with 100 nm-thick SiO<sub>2</sub> and a layout of 4  $\mu$ m gate length (L<sub>g</sub>) and 80  $\mu$ m gate width (L<sub>W</sub>) was used for electric characterization.

Illustrated in Fig. 3(a) are the representative output characteristics of TFT sample C having a Ga<sub>2</sub>O<sub>3</sub> layer thickness ratio R = 14.35%, corresponding to nominal single layer thickness of  $In_2O_3 = 3.71$  nm,  $Ga_2O_3 = 0.63$  nm and  $\rho_{\rm eff} = 9.2 \times 10^4 \ \Omega$  cm. We denote linear increase in the drain-to-source current  $(I_{DS})$  with respect to  $V_{DS}$ , followed by pinch-off and saturation of  $I_{\rm DS}$  with further increase of  $V_{DS}$ . From the log-plot of transfer curve in Fig. 3(b), one can denote an ON/OFF current ratio of  $1 \times 10^8$  and a subthreshold swing of S = 0.38 V/decade. One can further take advantage of the linear  $I_{\text{DS}}\text{-}V_{\text{GS}}$  characteristics to evaluate the transistor threshold voltage.<sup>15</sup> This was taken by linear interpolation of the  $I_{\rm DS}$  curve to intersect the  $V_{\rm GS}$  axis at  $I_{DS} = 0$ , which procedure shown in the inset of Fig. 3(b) renders  $V_T = 0.57$  V. One can further extract the transistor transconductance  $(g_m)$  according to  $g_m = \partial I_{DS} / \partial V_G$ . It can facilitate the derivation of field-effect mobility  $\mu_{FE}$  for TFT

$$\mu_{\rm FE} = (L_{\rm g} \times g_{\rm m}) / (L_{\rm W} \times C_{\rm OX} \times V_{\rm DS}) \tag{2}$$

This scenario leads to an increase of  $g_m$  with  $V_{GS}$  where maximum value of  $g_{m,max} = 277.2 \ \mu S$  can be observed at

TABLE I. Summary of the equivalent film resistivity and current ON/OFF ratio for TFT devices studied in Figs. 1(b) and 4 with various In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> thickness combination.

| TFT | $tIn_2O_3 (nm)/tGa_2O_3(nm)$ | Resistivity ( $\Omega$ cm) | I <sub>ON</sub> /I <sub>OFF</sub> ratio | TFT | $tIn_2O_3 (nm)/tGa_2O_3(nm)$ | Resistivity ( $\Omega$ cm) | I <sub>ON</sub> /I <sub>OFF</sub> ratio |

|-----|------------------------------|----------------------------|-----------------------------------------|-----|------------------------------|----------------------------|-----------------------------------------|

| A   | 4.06/0.54                    | $2.46 \times 10^{4}$       | 10                                      | F   | 3.64/0.81                    | $9.58 \times 10^{5}$       | $1.3 \times 10^4$                       |

| В   | 3.92/0.63                    | $4.88 \times 10^4$         | $1.0 \times 10^5$                       | G   | 3.50/0.90                    | $1.10 \times 10^6$         | $1.0 \times 10^4$                       |

| С   | 3.71/0.63                    | $9.20 	imes 10^4$          | $1.0 \times 10^8$                       | Н   | 3.36/0.99                    | $3.68 \times 10^{6}$       | $1.0 \times 10^4$                       |

| D   | 3.50/0.63                    | $1.43 \times 10^{5}$       | $4.8 \times 10^7$                       | Ι   | 3.22/1.08                    | $9.20 \times 10^{6}$       | $1.1 \times 10^4$                       |

| Е   | 3.80/0.70                    | $3.10 \times 10^{5}$       | $6.0 \times 10^5$                       |     |                              |                            |                                         |

(a)

los (mA/mm)

0.0

0.4

FIG. 2. (Color online) (a) Schematic layout of the MIS-capacitor sample B with 2 nm/30 nm  $Ga_2O_3/In_2O_3$ . (b) High and low C-V data on MIS-capacitor samples A/B and normalized to the  $Si_3N_4$  gate capacitance ( $C_i = 17.9$  pf). Inset: extracted interfacial trap charge density  $(D_{it})$  as a function of gate bias.

FIG. 3. (Color online) (a) Output and (b) transfer characteristics for In<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> TFT sample having an equivalent film resistivity  $\rho_{\rm eff} = 9.2 \times 10^4 \,\hat{\Omega}$  cm and  $Ga_2O_3$  layer thickness ratio R = 14.3%. Inset: (a) schematic layout of the TFT structure, (b) the extraction of threshold voltage

$V_{GS} = 1.5$  V and  $V_{DS} = 0.1$  V. Continued with parameter extraction using dielectric constant  $\varepsilon_r = 27.9$  for HfO<sub>2</sub> and  $C_{ox} = 2.7 \ \mu F/cm^2$  in Eq. (2),  $\mu_{FE}$  of 51.3 cm<sup>2</sup>/Vs can be derived at  $L_o/L_W = 4 \ \mu m/80 \ \mu m$ .

1.2

0.8 V<sub>DS</sub> (V)

0.9

1.6

10

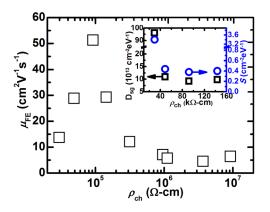

Further compiled in Fig. 4 are the extracted data of  $\mu_{\rm FE}$ for devices designed to have various Ga<sub>2</sub>O<sub>3</sub> layer thickness ratio R and hence difference in the film resistivity ( $\rho_{eff}$ ). The data were taken without post-growth annealing and measured at a low bias condition of  $V_{GS}\,{=}\,1.5$  V and  $V_{DS}\,{=}\,0.1$  V. Here, we denote an initial increase of  $\mu_{\rm FE}$  with  $\rho_{\rm eff}$  in the low-resistivity ( $10^4$ – $10^5 \Omega$  cm) regime, reaching a peak value of 51.3 cm<sup>2</sup>/Vs at  $\rho_{\rm eff} = 9.2 \times 10^4 \ \Omega$  cm, followed by rapid drop of  $\mu_{\rm FE}$  down to 5-10 cm<sup>2</sup>/Vs in the high-resistivity

FIG. 4. (Color online) Dependence of field-effect mobility ( $\mu_{\text{FE}}$ ) in In<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> TFTs having various Ga<sub>2</sub>O<sub>3</sub> layer thickness ratio R. Inset: the subthreshold swing S and the extracted trap density of the subgap states D<sub>so</sub> for devices at low gate bias ( $V_{GS} = 1.5$  V) and in the low resistivity regime  $(<10^5 \,\Omega \, cm).$

$(10^6 - 10^7 \ \Omega \ cm)$  regime. Similar behavior in the  $\mu$ - $\rho$  relation has been reported in the solution-processed In<sub>2</sub>O<sub>3</sub> TFTs annealed in air or in an  $O_2/O_3$  ambient,<sup>16</sup> or in the tin doped  $In_2O_3$  films deposited with various oxygen partial pressure.<sup>17</sup> Indeed the peak value of  $\mu_{\rm FE} = 51.3 \text{ cm}^2/\text{Vs}$  observed in this work is comparable to that of In2O3 TFT annealed at  $500 \,^{\circ}\text{C}$ ,<sup>16</sup> or in the doped In<sub>2</sub>O<sub>3</sub> film,<sup>17</sup> operated at a much large gate bias condition ( $V_{GS} > 15$  V). In comparison, our study on 50 nm-thick IGZO TFT with 2.8  $\times$  10<sup>4</sup>  $\Omega$  cm film resistivity and thick 35 nm-HfO<sub>2</sub>/15 nm-SiO<sub>2</sub> bottom-gate dielectric exhibits low value mobility  $\sim 8.9 \text{ cm}^2/\text{Vs}$  and high voltage operation characteristics of  $V_{DS} = 6$  and  $V_{GS} = 8$  V.<sup>18</sup>

100

′<sub>G</sub> (V)

We further note that in the low resistivity regime ( $<10^{5}$  $\Omega$  cm), increase of  $\mu_{\rm FE}$  is accompanied with an order of magnitude reduction in the transistor subthreshold swing (S) from 3.4 to 0.38 V/decade and improved ON/OFF current ratio from 10 to  $1 \times 10^8$  (data listed in Table I and inset of Fig. 4). Indeed, by correlating the trap density of subgap states  $(D_{SG})$  to the measured S value according to<sup>15</sup>

$$S = \ln 10 \cdot (k_{B}T/e) \cdot (1 + eD_{SG}/C_{OX}), \quad (3)$$

one can discern  $D_{SG}$  reduction from  $9.6 \times 10^{14}$  to  $9.2 \times 10^{13}$ / cm<sup>2</sup> eV. Under the low gate bias condition, these observations signify a trap-limited transport mechanism<sup>6</sup> upon which the reduced scattering centers due to annihilation of subgap states in the HfO<sub>2</sub>/In<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> bi-layer channel increases the device mobility and improve the ON/OFF current ratio.<sup>17</sup> Compared with our recent work on thick-dielectric HfO<sub>2</sub>/SiO<sub>2</sub>/IZGO TFT,<sup>18</sup> it reveals the advantages of using thin high-k dielectric to reduce the operation voltage and thin Ga<sub>2</sub>O<sub>3</sub> layers to suppress  $D_{sg}$  and enhance  $\mu_{FE}$ .

In summary, we demonstrated a device concept using the layer thickness modulation in an  $In_2O_3/Ga_2O_3$  bi-layer stack channel to achieve enhancement mode operation of TFT ( $V_T = 0.57$  V) with high field-effect mobility ( $\mu_{FE} = 51.3 \text{ cm}^2/\text{Vs}$ ), low subthreshold swing (S = 0.38 V/dec) and ON/OFF current ratio of  $10^8$ . At low gate bias and low resistivity regime, these observations are ascribed to a traplimited transport mechanism upon which the reduced trap density of the subgap states dominates in the device electric properties.

This research was supported by the National Science Council Grant 98-2221-E-002-021-MY3, 98-2923-E-002-001-MY3, 100-2120 -M-002-017-CC1, and NTU Excellent Research Project (10R80908).

<sup>2</sup>M. Tsukude, S. Akamatsu, S. Miyazaki, and M. Hirose, Jpn. J. Appl. Phys. **26**, L111 (1987).

<sup>3</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature **432**, 488 (2004).

<sup>4</sup>M. Kimura, T. Kamiya, T. Nakanishi, K. Nomura, and H. Hosono, Appl. Phys. Lett. 96, 262105 (2010).

- <sup>5</sup>M. Grundmann, H. Frenzel, A. Lajn, M. Lorenz, F. Schein, and H. von Wenckstern, Phys. Status Solidi A **207**, 1437 (2010).

- <sup>6</sup>S. Lee, K. Ghaffarzadeh, A. Nathan, J. Robertson, S. Jeon, C. Kim, I.-H. Song, and U.-I. Chung, Appl. Phys. Lett. 98, 203508 (2011).

- <sup>7</sup>R. Martins, P. Barquinha, I. Ferreira, L. Pereira, G. Goçnalves, and E. Fortunato, J. Appl. Phys. **101**, 044505 (2007).

- <sup>8</sup>H.-K. Noh, K. J. Chang, B. Ryu, and W.-J. Lee, Phys. Rev. B **84**, 115205 (2011).

- <sup>9</sup>T. Kamiya, K. Nomura, and H. Hosono, Phys. Status Solidi A **207**, 1698 (2010).

- <sup>10</sup>T. Iwasaki, N. Itagaki, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, Appl. Phys. Lett. **90**, 242114 (2007).

- <sup>11</sup>Y.-H. Kim, M.-K. Han, J.-I. Han, and S. K. Park, IEEE Trans. Electron Devices **57**, 1009 (2010).

- <sup>12</sup>D. K. Schroder, in *Semiconductor Material Device Characterization*, 2nd ed. (John Wiley & Sons, Inc., New York, 1998), Chap. 4.

- <sup>13</sup>E. H. Nicollian and J. R. Brews, in *MOS Physics and Technology* (Wiley, New York, 1982), Chap. 10.

- <sup>14</sup>J. H. Kim, U. K. Kim, Y. J. Chung, and C. S. Hwang, Appl. Phys. Lett. 98, 23102 (2011).

- <sup>15</sup>T. Kamiya, K. Nomura, and H. Hosono, Sci. Technol. Adv. Mater. 11, 044305 (2010).

- <sup>16</sup>S.-Y. Han, G. S. Herman, and C.-H. Chang, J. Am. Chem. Soc. **133**, 5166 (2011).

- <sup>17</sup>C.-H. Chung, Y.-W. Ko, Y.-H. Kim, C.-Y. Sohn, H. Y. Chu, S.-H. Ko Park, and J. H. Lee, Thin Solid Films **491**, 294 (2005).

- <sup>18</sup>L.-Y. Su, H.-Y. Lin, H.-K. Lin, S.-L, Wang, L.-H. Peng, and J.-J. Huang, IEEE Electron Device Lett. **32**, 1245 (2011).

<sup>&</sup>lt;sup>1</sup>C. Y. Kagan and P. W. E. Andry, *Thin Film Transistors* (Dekker, New York, 2003).